Macros | |

| #define | LTC_CMD_WRCFGA (0x1) |

| #define | LTC_CMD_WRCFGA_0_GPIO_PULLUP(gpio) ((1 << gpio) << 3) |

| #define | LTC_CMD_WRCFGA_0_REFON BIT(2) |

| #define | LTC_CMD_WRCFGA_0_DTEN BIT(1) |

| #define | LTC_CMD_WRCFGA_0_ADCOPT BIT(0) |

| #define | LTC_CMD_WRCFGA_4_DCC(x) BIT(x) |

| #define | LTC_CMD_WRCFGA_5_DCTO(DCTO) (DCTO << 4) |

| #define | LTC_CMD_RDCFGA (0x2) |

| #define | LTC_CMD_RDCVA (0x4) |

| #define | LTC_CMD_RDCVB (0x6) |

| #define | LTC_CMD_RDCVC (0x8) |

| #define | LTC_CMD_RDCVD (0xA) |

| #define | LTC_CMD_RDAUXA (0xC) |

| #define | LTC_CMD_RDAUXB (0xE) |

| #define | LTC_CMD_RDSTATA (0x10) |

| #define | LTC_CMD_RDSTATB (0x12) |

| #define | LTC_CMD_WRSCTRL (0x14) |

| #define | LTC_CMD_WRPWM (0x20) |

| #define | LTC_CMD_RDSCTRL (0x16) |

| #define | LTC_CMD_RDPWM (0x22) |

| #define | LTC_CMD_STSCTRL (0x19) |

| #define | LTC_CMD_CLRSCTRL (0x18) |

| #define | LTC_CMD_ADCV(CH, DCP, MD) (BIT(5) | BIT(6) | BIT(9) | (((CH) & 0x7) << 0) | (((DCP) & 0x1) << 4) | (((MD) & 0x3) << 7)) |

| #define | LTC_CMD_ADCV_NORM_DCP_ALL (0x370) |

| #define | LTC_CMD_ADOW(CH, DCP, PUP, MD) (BIT(3) | BIT(5) | BIT(9) | (((CH) & 0x7) << 0) |(((PUP) & 0x1) << 6) ((DCP & 0x1) << 4) | (((MD) & 0x3) << 7)) |

| #define | LTC_CMD_ADOW_NORM_PUP_ALL (0x378) |

| #define | LTC_CMD_ADOW_NORM_PDN_ALL (0x338) |

| #define | LTC_CMD_CVST(ST, MD) (BIT(0) | BIT(1) | BIT(2) | BIT(9) | (((ST) & 0x3) << 5) | (((MD) & 0x3) << 7)) |

| #define | LTC_CMD_CVST_NORM_ST1 (0x327) |

| #define | LTC_CMD_ADOL(DCP, MD) (BIT(0) | BIT(9) | (((DCP) & 0x1) << 4) | (((MD) & 0x3) << 7)) |

| #define | LTC_CMD_ADOL_NORM_DCP (0x311) |

| #define | LTC_CMD_ADAX(CHG, MD) (BIT(5) | BIT(6) | BIT(10) | (((CHG) & 0x7) << 0) | (((MD & 0x3) << 7))) |

| #define | LTC_CMD_ADAX_NORM_GPIO1 (0x561) |

| #define | LTC_CMD_ADAX_NORM_GPIO2 (0x562) |

| #define | LTC_CMD_ADAXD(CHG, MD) (BIT(10) | (((CHG) & 0x7) << 0) | (((MD & 0x3) << 7))) |

| #define | LTC_CMD_ADAXD_NORM_GPIO1 (0x501) |

| #define | LTC_CMD_ADAXD_NORM_GPIO2 (0x502) |

| #define | LTC_CMD_AXST(ST, MD) (BIT(0) | BIT(1) | BIT(2) | BIT(10) | (((ST) & 0x3) << 5) | (((MD) & 0x3) << 7)) |

| #define | LTC_CMD_AXST_NORM_ST1 (0x527) |

| #define | LTC_CMD_ADSTAT(CHST, MD) (BIT(3) | BIT(5) | BIT(6) | BIT(10) | (((CHST) & 0x7) << 0) | (((MD) & 0x3) << 7)) |

| #define | LTC_CMD_ADSTAT_NORM_ALL (0x568) |

| #define | LTC_CMD_ADSTATD(CHST, MD) (BIT(3) | BIT(10) | (((CHST) & 0x7) << 0) | (((MD) & 0x3) << 7)) |

| #define | LTC_CMD_ADSTATD_NORM_ALL (0x508) |

| #define | LTC_CMD_STATST(ST, MD) (BIT(0) | BIT(1) | BIT(2) | BIT(3) | BIT(10) | (((ST) & 0x3) << 5) | (((MD) & 0x3) << 7)) |

| #define | LTC_CMD_STATST_NORM_ST1 (0x52F) |

| #define | LTC_CMD_ADCVAX(DCP, MD) (BIT(0) | BIT(1) | BIT(2) | BIT(3) | BIT(6) | BIT(10) | (((DCP) & 0x1) << 4) | (((MD) & 0x3) << 7)) |

| #define | LTC_CMD_ADCVAX_NORM_DCP (0x57F) |

| #define | LTC_CMD_ADCVSC(DCP, MD) (BIT(0) | BIT(1) | BIT(2) | BIT(6) | BIT(10) | (((DCP) & 0x1) << 4) | (((MD) & 0x3) << 7)) |

| #define | LTC_CMD_ADCVSC_NORM_DCP (0x577) |

| #define | LTC_CMD_CLRCELL (0x711) |

| #define | LTC_CMD_CLRAUX (0x712) |

| #define | LTC_CMD_CLRSTAT (0x713) |

| #define | LTC_CMD_PLADC (0x714) |

| #define | LTC_CMD_DIAGN (0x715) |

| #define | LTC_CMD_WRCOMM (0x721) |

| #define | LTC_CMD_RDCOMM (0x722) |

| #define | LTC_CMD_STCOMM (0x723) |

| #define | LTC6811_ADDDEV(id, numberofslave, _cellUnderVoltage, _cellOverVoltage) |

| #define | LTC6811_SLAVE_ADDDEV(masterid, id) |

| #define | LTC6811_ID(id) HAL_GET_ID(hal, ltc6811, ltc6811_dev_##id) |

| #define | LTC6811_SLAVE_ID(masterid, id) HAL_GET_ID(hal, ltc6811, ltc6811_slave_##masterid##_##id) |

| #define | LTC6811_ADC_ID(masterid, id, adcid) HAL_GET_ID(adc, ltc6811, ltc6811_adc_##masterid##_##id##_##adcid) |

| #define | LTC6811_GET_ALL_ADCS(masterid, id, adcs) |

Typedefs | |

| typedef int16_t | ltc_cmd_t |

Functions | |

| struct ltc6811 * | ltc6811_init (uint32_t index) |

| struct ltc6811_slave * | ltc6811_slave_init (uint32_t index) |

| int32_t | ltc6811_connect (struct ltc6811 *ltc, struct spi *spi, uint8_t cs, uint16_t gpio, uint32_t baudrate) |

| int32_t | ltc6811_write (struct ltc6811 *ltc, ltc_cmd_t cmd, uint8_t *data, uint32_t len) |

| int32_t | ltc6811_read (struct ltc6811 *ltc, ltc_cmd_t cmd, uint8_t *data, uint32_t len) |

| uint16_t | ltc6811_calcPEC (uint8_t *data, uint8_t len) |

| int32_t | ltc6811_writeRegister (struct ltc6811 *ltc, ltc_cmd_t cmd, uint8_t *newData, uint8_t *oldData) |

| int32_t | ltc6811_readRegister (struct ltc6811 *ltc, ltc_cmd_t cmd, uint8_t *registerContent) |

| int32_t | ltc6811_setADCCallback (struct ltc6811 *ltc, bool(*callback)(struct ltc6811 *ltc, void *data), void *data) |

| int32_t | ltc6811_startADC (struct ltc6811 *ltc) |

| int32_t | ltc6811_stopADC (struct ltc6811 *ltc) |

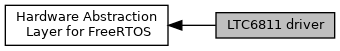

Detailed Description

This is the LTC6811 Driver.

Macro Definition Documentation

◆ LTC6811_ADC_ID

| #define LTC6811_ADC_ID | ( | masterid, | |

| id, | |||

| adcid | |||

| ) | HAL_GET_ID(adc, ltc6811, ltc6811_adc_##masterid##_##id##_##adcid) |

◆ LTC6811_ADDDEV

| #define LTC6811_ADDDEV | ( | id, | |

| numberofslave, | |||

| _cellUnderVoltage, | |||

| _cellOverVoltage | |||

| ) |

◆ LTC6811_GET_ALL_ADCS

| #define LTC6811_GET_ALL_ADCS | ( | masterid, | |

| id, | |||

| adcs | |||

| ) |

◆ LTC6811_ID

| #define LTC6811_ID | ( | id | ) | HAL_GET_ID(hal, ltc6811, ltc6811_dev_##id) |

◆ LTC6811_SLAVE_ADDDEV

| #define LTC6811_SLAVE_ADDDEV | ( | masterid, | |

| id | |||

| ) |

◆ LTC6811_SLAVE_ID

| #define LTC6811_SLAVE_ID | ( | masterid, | |

| id | |||

| ) | HAL_GET_ID(hal, ltc6811, ltc6811_slave_##masterid##_##id) |

◆ LTC_CMD_ADAX

| #define LTC_CMD_ADAX | ( | CHG, | |

| MD | |||

| ) | (BIT(5) | BIT(6) | BIT(10) | (((CHG) & 0x7) << 0) | (((MD & 0x3) << 7))) |

Start GPIOs ADC Conversion and Poll Status (ADAX)

- Parameters

-

CHG GPIO Selection for ADC Conversion CHG Total Conversion Time in the 8 ADC Modes 27kHz 14kHz 7kHz 3kHz 2kHz 1kHz 422Hz 26Hz 000 GPIO 1-5, 2nd Ref 1.1ms 1.3ms 2.3ms 3.0ms 4.4ms 7.2ms 12.8ms 201ms 001 GPIO 1 201μs 230μs 405μs 501μs 754μs 1.2ms 2.2ms 34ms 010 GPIO 2 011 GPIO 3 100 GPIO 4 101 GPIO 5 110 2 nd Reference MD ADC Mode MD ADCOPT(CFGR0[0]) = 0 ADCOPT(CFGR0[0]) = 1 00 422Hz Mode 1kHz Mode 01 27kHz Mode (Fast) 14kHz Mode 10 7kHz Mode (Normal) 3kHz Mode 11 26Hz Mode (Filtered) 2kHz Mode

◆ LTC_CMD_ADAX_NORM_GPIO1

| #define LTC_CMD_ADAX_NORM_GPIO1 (0x561) |

◆ LTC_CMD_ADAX_NORM_GPIO2

| #define LTC_CMD_ADAX_NORM_GPIO2 (0x562) |

◆ LTC_CMD_ADAXD

| #define LTC_CMD_ADAXD | ( | CHG, | |

| MD | |||

| ) | (BIT(10) | (((CHG) & 0x7) << 0) | (((MD & 0x3) << 7))) |

Start GPIOs ADC Conversion With Digital Redundancy and Poll Status (ADAXD)

- Parameters

-

CHG GPIO Selection for ADC Conversion CHG Total Conversion Time in the 8 ADC Modes 27kHz 14kHz 7kHz 3kHz 2kHz 1kHz 422Hz 26Hz 000 GPIO 1-5, 2nd Ref 1.1ms 1.3ms 2.3ms 3.0ms 4.4ms 7.2ms 12.8ms 201ms 001 GPIO 1 201μs 230μs 405μs 501μs 754μs 1.2ms 2.2ms 34ms 010 GPIO 2 011 GPIO 3 100 GPIO 4 101 GPIO 5 110 2 nd Reference MD ADC Mode MD ADCOPT(CFGR0[0]) = 0 ADCOPT(CFGR0[0]) = 1 00 422Hz Mode 1kHz Mode 01 27kHz Mode (Fast) 14kHz Mode 10 7kHz Mode (Normal) 3kHz Mode 11 26Hz Mode (Filtered) 2kHz Mode

◆ LTC_CMD_ADAXD_NORM_GPIO1

| #define LTC_CMD_ADAXD_NORM_GPIO1 (0x501) |

◆ LTC_CMD_ADAXD_NORM_GPIO2

| #define LTC_CMD_ADAXD_NORM_GPIO2 (0x502) |

◆ LTC_CMD_ADCV

| #define LTC_CMD_ADCV | ( | CH, | |

| DCP, | |||

| MD | |||

| ) | (BIT(5) | BIT(6) | BIT(9) | (((CH) & 0x7) << 0) | (((DCP) & 0x1) << 4) | (((MD) & 0x3) << 7)) |

Start Cell Voltage ADC Conversion and Poll Status (ADCV)

- Parameters

-

CH Cell Selection for ADC Conversion CH Total Conversion Time in the 8 ADC Modes 27kHz 14kHz 7kHz 3kHz 2kHz 1kHz 422Hz 26Hz 000 All Cells 1.1ms 1.3ms 2.3ms 3.0ms 4.4ms 7.2ms 12.8ms 201ms 001 Cell 1 and Cell 7 201μs 230μs 405μs 501μs 754μs 1.2ms 2.2ms 34ms 010 Cell 2 and Cell 8 011 Cell 3 and Cell 9 100 Cell 4 and Cell 10 101 Cell 5 and Cell 11 110 Cell 6 and Cell 12 DCP Discharge Permitted 0 = Discharge Not Permitted 1 = Discharge Permitted MD ADC Mode MD ADCOPT(CFGR0[0]) = 0 ADCOPT(CFGR0[0]) = 1 00 422Hz Mode 1kHz Mode 01 27kHz Mode (Fast) 14kHz Mode 10 7kHz Mode (Normal) 3kHz Mode 11 26Hz Mode (Filtered) 2kHz Mode

◆ LTC_CMD_ADCV_NORM_DCP_ALL

| #define LTC_CMD_ADCV_NORM_DCP_ALL (0x370) |

◆ LTC_CMD_ADCVAX

| #define LTC_CMD_ADCVAX | ( | DCP, | |

| MD | |||

| ) | (BIT(0) | BIT(1) | BIT(2) | BIT(3) | BIT(6) | BIT(10) | (((DCP) & 0x1) << 4) | (((MD) & 0x3) << 7)) |

Start Combined Cell Voltage and GPIO1, GPIO2 Conversion and Poll Status (ADCVAX)

- Parameters

-

DCP Discharge Permitted 0 = Discharge Not Permitted 1 = Discharge Permitted MD ADC Mode MD ADCOPT(CFGR0[0]) = 0 ADCOPT(CFGR0[0]) = 1 00 422Hz Mode 1kHz Mode 01 27kHz Mode (Fast) 14kHz Mode 10 7kHz Mode (Normal) 3kHz Mode 11 26Hz Mode (Filtered) 2kHz Mode

◆ LTC_CMD_ADCVAX_NORM_DCP

| #define LTC_CMD_ADCVAX_NORM_DCP (0x57F) |

◆ LTC_CMD_ADCVSC

| #define LTC_CMD_ADCVSC | ( | DCP, | |

| MD | |||

| ) | (BIT(0) | BIT(1) | BIT(2) | BIT(6) | BIT(10) | (((DCP) & 0x1) << 4) | (((MD) & 0x3) << 7)) |

Start Combined Cell Voltage and SC Conversion and Poll Status (ADCVSC)

- Parameters

-

DCP Discharge Permitted 0 = Discharge Not Permitted 1 = Discharge Permitted MD ADC Mode MD ADCOPT(CFGR0[0]) = 0 ADCOPT(CFGR0[0]) = 1 00 422Hz Mode 1kHz Mode 01 27kHz Mode (Fast) 14kHz Mode 10 7kHz Mode (Normal) 3kHz Mode 11 26Hz Mode (Filtered) 2kHz Mode

◆ LTC_CMD_ADCVSC_NORM_DCP

| #define LTC_CMD_ADCVSC_NORM_DCP (0x577) |

◆ LTC_CMD_ADOL

Start Overlap Measurement of Cell 7 Voltage (ADOL)

- Parameters

-

DCP Discharge Permitted 0 = Discharge Not Permitted 1 = Discharge Permitted MD ADC Mode MD ADCOPT(CFGR0[0]) = 0 ADCOPT(CFGR0[0]) = 1 00 422Hz Mode 1kHz Mode 01 27kHz Mode (Fast) 14kHz Mode 10 7kHz Mode (Normal) 3kHz Mode 11 26Hz Mode (Filtered) 2kHz Mode

◆ LTC_CMD_ADOL_NORM_DCP

| #define LTC_CMD_ADOL_NORM_DCP (0x311) |

◆ LTC_CMD_ADOW

| #define LTC_CMD_ADOW | ( | CH, | |

| DCP, | |||

| PUP, | |||

| MD | |||

| ) | (BIT(3) | BIT(5) | BIT(9) | (((CH) & 0x7) << 0) |(((PUP) & 0x1) << 6) ((DCP & 0x1) << 4) | (((MD) & 0x3) << 7)) |

Start Open Wire ADC Conversion and Poll Status ADOW 0 1 1 1 (PUP)

- Parameters

-

CH Cell Selection for ADC Conversion CH Total Conversion Time in the 8 ADC Modes 27kHz 14kHz 7kHz 3kHz 2kHz 1kHz 422Hz 26Hz 000 All Cells 1.1ms 1.3ms 2.3ms 3.0ms 4.4ms 7.2ms 12.8ms 201ms 001 Cell 1 and Cell 7 201μs 230μs 405μs 501μs 754μs 1.2ms 2.2ms 34ms 010 Cell 2 and Cell 8 011 Cell 3 and Cell 9 100 Cell 4 and Cell 10 101 Cell 5 and Cell 11 110 Cell 6 and Cell 12 DCP Discharge Permitted 0 = Discharge Not Permitted 1 = Discharge Permitted PUP Pull-Up/Pull-Down Current for Open Wire Conversions 0 = Pull-Down Current 1 = Pull-Up Current MD ADC Mode MD ADCOPT(CFGR0[0]) = 0 ADCOPT(CFGR0[0]) = 1 00 422Hz Mode 1kHz Mode 01 27kHz Mode (Fast) 14kHz Mode 10 7kHz Mode (Normal) 3kHz Mode 11 26Hz Mode (Filtered) 2kHz Mode

◆ LTC_CMD_ADOW_NORM_PDN_ALL

| #define LTC_CMD_ADOW_NORM_PDN_ALL (0x338) |

◆ LTC_CMD_ADOW_NORM_PUP_ALL

| #define LTC_CMD_ADOW_NORM_PUP_ALL (0x378) |

◆ LTC_CMD_ADSTAT

| #define LTC_CMD_ADSTAT | ( | CHST, | |

| MD | |||

| ) | (BIT(3) | BIT(5) | BIT(6) | BIT(10) | (((CHST) & 0x7) << 0) | (((MD) & 0x3) << 7)) |

Start Status Group ADC Conversion and Poll Status (ADSTAT)

- Parameters

-

CHST Status Group Selection CHST Total Conversion Time in the 8 ADC Modes 27kHz 14kHz 7kHz 3kHz 2kHz 1kHz 422Hz 26Hz 000 SC, ITMP, VA, VD 748μs 865μs 1.6ms 2.0ms 3.0ms 4.8ms 8.5ms 134ms 001 SC 201μs 230μs 405μs 501μs 754μs 1.2ms 2.2ms 34ms 010 ITMP 011 VA 100 VD MD ADC Mode MD ADCOPT(CFGR0[0]) = 0 ADCOPT(CFGR0[0]) = 1 00 422Hz Mode 1kHz Mode 01 27kHz Mode (Fast) 14kHz Mode 10 7kHz Mode (Normal) 3kHz Mode 11 26Hz Mode (Filtered) 2kHz Mode

◆ LTC_CMD_ADSTAT_NORM_ALL

| #define LTC_CMD_ADSTAT_NORM_ALL (0x568) |

◆ LTC_CMD_ADSTATD

| #define LTC_CMD_ADSTATD | ( | CHST, | |

| MD | |||

| ) | (BIT(3) | BIT(10) | (((CHST) & 0x7) << 0) | (((MD) & 0x3) << 7)) |

Start Status Group ADC Conversion With Digital Redundancy and Poll Status (ADSTATD)

- Parameters

-

CHST Status Group Selection CHST Total Conversion Time in the 8 ADC Modes 27kHz 14kHz 7kHz 3kHz 2kHz 1kHz 422Hz 26Hz 000 SC, ITMP, VA, VD 748μs 865μs 1.6ms 2.0ms 3.0ms 4.8ms 8.5ms 134ms 001 SC 201μs 230μs 405μs 501μs 754μs 1.2ms 2.2ms 34ms 010 ITMP 011 VA 100 VD MD ADC Mode MD ADCOPT(CFGR0[0]) = 0 ADCOPT(CFGR0[0]) = 1 00 422Hz Mode 1kHz Mode 01 27kHz Mode (Fast) 14kHz Mode 10 7kHz Mode (Normal) 3kHz Mode 11 26Hz Mode (Filtered) 2kHz Mode

◆ LTC_CMD_ADSTATD_NORM_ALL

| #define LTC_CMD_ADSTATD_NORM_ALL (0x508) |

◆ LTC_CMD_AXST

| #define LTC_CMD_AXST | ( | ST, | |

| MD | |||

| ) | (BIT(0) | BIT(1) | BIT(2) | BIT(10) | (((ST) & 0x3) << 5) | (((MD) & 0x3) << 7)) |

Start Self Test GPIOs Conversion and Poll Status (AXST)

- Parameters

-

ST Self Test Mode Selection ST Self Test Conversion Result 27kHz 14kHz 7kHz 3kHz 2kHz 1kHz 422Hz 26Hz 01 Self Test 1 0x9565 0x9553 0x9555 0x9555 0x9555 0x9555 0x9555 0x9555 10 Self Test 2 0x6A9A 0x6AAC 0x6AAA 0x6AAA 0x6AAA 0x6AAA 0x6AAA 0x6AAA MD ADC Mode MD ADCOPT(CFGR0[0]) = 0 ADCOPT(CFGR0[0]) = 1 00 422Hz Mode 1kHz Mode 01 27kHz Mode (Fast) 14kHz Mode 10 7kHz Mode (Normal) 3kHz Mode 11 26Hz Mode (Filtered) 2kHz Mode

◆ LTC_CMD_AXST_NORM_ST1

| #define LTC_CMD_AXST_NORM_ST1 (0x527) |

◆ LTC_CMD_CLRAUX

| #define LTC_CMD_CLRAUX (0x712) |

Clear Auxiliary Register Groups (CLRAUX)

◆ LTC_CMD_CLRCELL

| #define LTC_CMD_CLRCELL (0x711) |

Clear Cell Voltage Register Groups (CLRCELL)

◆ LTC_CMD_CLRSCTRL

| #define LTC_CMD_CLRSCTRL (0x18) |

Clear S Control Register Group (CLRSCTRL)

◆ LTC_CMD_CLRSTAT

| #define LTC_CMD_CLRSTAT (0x713) |

Clear Status Register Groups (CLRSTAT)

◆ LTC_CMD_CVST

| #define LTC_CMD_CVST | ( | ST, | |

| MD | |||

| ) | (BIT(0) | BIT(1) | BIT(2) | BIT(9) | (((ST) & 0x3) << 5) | (((MD) & 0x3) << 7)) |

Start Self Test Cell Voltage Conversion and Poll Status (CVST)

- Parameters

-

ST Self Test Mode Selection ST Self Test Conversion Result 27kHz 14kHz 7kHz 3kHz 2kHz 1kHz 422Hz 26Hz 01 Self Test 1 0x9565 0x9553 0x9555 0x9555 0x9555 0x9555 0x9555 0x9555 10 Self Test 2 0x6A9A 0x6AAC 0x6AAA 0x6AAA 0x6AAA 0x6AAA 0x6AAA 0x6AAA MD ADC Mode MD ADCOPT(CFGR0[0]) = 0 ADCOPT(CFGR0[0]) = 1 00 422Hz Mode 1kHz Mode 01 27kHz Mode (Fast) 14kHz Mode 10 7kHz Mode (Normal) 3kHz Mode 11 26Hz Mode (Filtered) 2kHz Mode

◆ LTC_CMD_CVST_NORM_ST1

| #define LTC_CMD_CVST_NORM_ST1 (0x327) |

◆ LTC_CMD_DIAGN

| #define LTC_CMD_DIAGN (0x715) |

Diagnose MUX and Poll Status (DIAGN)

◆ LTC_CMD_PLADC

| #define LTC_CMD_PLADC (0x714) |

Poll ADC Conversion Status (PLADC)

◆ LTC_CMD_RDAUXA

| #define LTC_CMD_RDAUXA (0xC) |

Read Auxiliary Register Group A (RDAUXA)

◆ LTC_CMD_RDAUXB

| #define LTC_CMD_RDAUXB (0xE) |

Read Auxiliary Register Group B (RDAUXB)

◆ LTC_CMD_RDCFGA

| #define LTC_CMD_RDCFGA (0x2) |

Read Configuration Register Group A (RDCFGA)

◆ LTC_CMD_RDCOMM

| #define LTC_CMD_RDCOMM (0x722) |

Read COMM Register Group (RDCOMM)

◆ LTC_CMD_RDCVA

| #define LTC_CMD_RDCVA (0x4) |

Read Cell Voltage Register Group A (RDCVA)

◆ LTC_CMD_RDCVB

| #define LTC_CMD_RDCVB (0x6) |

Read Cell Voltage Register Group B (RDCVB)

◆ LTC_CMD_RDCVC

| #define LTC_CMD_RDCVC (0x8) |

Read Cell Voltage Register Group C (RDCVC)

◆ LTC_CMD_RDCVD

| #define LTC_CMD_RDCVD (0xA) |

Read Cell Voltage Register Group D (RDCVD)

◆ LTC_CMD_RDPWM

| #define LTC_CMD_RDPWM (0x22) |

Read PWM Register Group (RDPWM)

◆ LTC_CMD_RDSCTRL

| #define LTC_CMD_RDSCTRL (0x16) |

Read S Control Register Group (RDSCTRL)

◆ LTC_CMD_RDSTATA

| #define LTC_CMD_RDSTATA (0x10) |

Read Status Register Group A (RDSTATA)

◆ LTC_CMD_RDSTATB

| #define LTC_CMD_RDSTATB (0x12) |

Read Status Register Group B (RDSTATB)

◆ LTC_CMD_STATST

| #define LTC_CMD_STATST | ( | ST, | |

| MD | |||

| ) | (BIT(0) | BIT(1) | BIT(2) | BIT(3) | BIT(10) | (((ST) & 0x3) << 5) | (((MD) & 0x3) << 7)) |

Start Self Test Status Group Conversion and Poll Status (STATST)

- Parameters

-

ST Self Test Mode Selection ST Self Test Conversion Result 27kHz 14kHz 7kHz 3kHz 2kHz 1kHz 422Hz 26Hz 01 Self Test 1 0x9565 0x9553 0x9555 0x9555 0x9555 0x9555 0x9555 0x9555 10 Self Test 2 0x6A9A 0x6AAC 0x6AAA 0x6AAA 0x6AAA 0x6AAA 0x6AAA 0x6AAA MD ADC Mode MD ADCOPT(CFGR0[0]) = 0 ADCOPT(CFGR0[0]) = 1 00 422Hz Mode 1kHz Mode 01 27kHz Mode (Fast) 14kHz Mode 10 7kHz Mode (Normal) 3kHz Mode 11 26Hz Mode (Filtered) 2kHz Mode

◆ LTC_CMD_STATST_NORM_ST1

| #define LTC_CMD_STATST_NORM_ST1 (0x52F) |

◆ LTC_CMD_STCOMM

| #define LTC_CMD_STCOMM (0x723) |

Start Communication I2C/SPI (STCOMM)

◆ LTC_CMD_STSCTRL

| #define LTC_CMD_STSCTRL (0x19) |

Start S Control Pulsing and Poll Status (STSCTRL)

◆ LTC_CMD_WRCFGA

| #define LTC_CMD_WRCFGA (0x1) |

Write Configuration Register Group A (WRCFGA)

◆ LTC_CMD_WRCFGA_0_ADCOPT

| #define LTC_CMD_WRCFGA_0_ADCOPT BIT(0) |

ADC Mode Option Bit 0 -> Selects Modes 27kHz, 7kHz, 422Hz or 26Hz with MD[1:0] Bits in ADC Conversion Commands (Default) 1 -> Selects Modes 14kHz, 3kHz, 1kHz or 2kHz with MD[1:0] Bits in ADC Conversion Commands

◆ LTC_CMD_WRCFGA_0_DTEN

| #define LTC_CMD_WRCFGA_0_DTEN BIT(1) |

Discharge Timer Enable (Read Only) 1 -> Enables the Discharge Timer for Discharge Switches 0 -> Disables Discharge Timer

◆ LTC_CMD_WRCFGA_0_GPIO_PULLUP

| #define LTC_CMD_WRCFGA_0_GPIO_PULLUP | ( | gpio | ) | ((1 << gpio) << 3) |

Define GPIO Pullup

- Parameters

-

gpio 0 = GPIO1, 1 = GPIO2, etc

◆ LTC_CMD_WRCFGA_0_REFON

| #define LTC_CMD_WRCFGA_0_REFON BIT(2) |

References Powered Up

1 = References Remain Powered Up Until Watchdog Timeout 0 = References Shut Down After Conversions

◆ LTC_CMD_WRCFGA_4_DCC

| #define LTC_CMD_WRCFGA_4_DCC | ( | x | ) | BIT(x) |

Discharge Cell

- Parameters

-

Cell 0 - 11 (16 Bit Acces!)

◆ LTC_CMD_WRCFGA_5_DCTO

| #define LTC_CMD_WRCFGA_5_DCTO | ( | DCTO | ) | (DCTO << 4) |

Discharge Timeout Value

- Parameters

-

DCTO 0x0-0xF DCTO 0 1 2 3 4 5 6 7 8 9 A B C D E F Time (MIN) Disabled 0.5 1 2 3 4 5 10 15 20 30 40 60 75 90 120

◆ LTC_CMD_WRCOMM

| #define LTC_CMD_WRCOMM (0x721) |

Write COMM Register Group (WRCOMM)

◆ LTC_CMD_WRPWM

| #define LTC_CMD_WRPWM (0x20) |

Write PWM Register Group (WRPWM)

◆ LTC_CMD_WRSCTRL

| #define LTC_CMD_WRSCTRL (0x14) |

Write S Control Register Group (WRSCTRL)

Typedef Documentation

◆ ltc_cmd_t

| typedef int16_t ltc_cmd_t |

CMD

Function Documentation

◆ ltc6811_calcPEC()

| uint16_t ltc6811_calcPEC | ( | uint8_t * | data, |

| uint8_t | len | ||

| ) |

Calc PEC of Payload

- Parameters

-

data Data len Len of data

- Returns

- PEC

◆ ltc6811_connect()

| int32_t ltc6811_connect | ( | struct ltc6811 * | ltc, |

| struct spi * | spi, | ||

| uint8_t | cs, | ||

| uint16_t | gpio, | ||

| uint32_t | baudrate | ||

| ) |

Connect LTC6811 to spi Bus

- Parameters

-

ltc LTC6811 Instance spi SPI Master cs CS Number or SPI_OPT_CS_DIS gpio GPIO Pin Number or SPI_OPT_GPIO_DIS baudrate Baudrate

- Returns

- -1 on error 0 on ok

◆ ltc6811_init()

| struct ltc6811* ltc6811_init | ( | uint32_t | index | ) |

Init LTC6811

- Parameters

-

index Driver Index

- Returns

- LTC6811 Instance or NULL on error

◆ ltc6811_read()

| int32_t ltc6811_read | ( | struct ltc6811 * | ltc, |

| ltc_cmd_t | cmd, | ||

| uint8_t * | data, | ||

| uint32_t | len | ||

| ) |

Read from LTC6811 in dasy-chain!

- Parameters

-

ltc LTC6811 Instance cmd Command PEC is generated automatically data Data to send PEC is not generated! Proper size must be selected to send to all Slave in the chain! len Size of Data

- Returns

- -1 on error 0 on ok

◆ ltc6811_readRegister()

| int32_t ltc6811_readRegister | ( | struct ltc6811 * | ltc, |

| ltc_cmd_t | cmd, | ||

| uint8_t * | registerContent | ||

| ) |

Read from all LTC6811 Register

- Parameters

-

ltc LTC6811 Instance cmd Command PEC is checked automatically registerContent Array must be 6 bytes! * Number of Slaves

- Returns

- -1 on error 0 on ok

◆ ltc6811_setADCCallback()

| int32_t ltc6811_setADCCallback | ( | struct ltc6811 * | ltc, |

| bool(*)(struct ltc6811 *ltc, void *data) | callback, | ||

| void * | data | ||

| ) |

◆ ltc6811_slave_init()

| struct ltc6811_slave* ltc6811_slave_init | ( | uint32_t | index | ) |

Init LTC6811 Slave

- Parameters

-

index Driver Index

- Returns

- LTC6811 Slave Instance or NULL on error

◆ ltc6811_startADC()

| int32_t ltc6811_startADC | ( | struct ltc6811 * | ltc | ) |

◆ ltc6811_stopADC()

| int32_t ltc6811_stopADC | ( | struct ltc6811 * | ltc | ) |

◆ ltc6811_write()

| int32_t ltc6811_write | ( | struct ltc6811 * | ltc, |

| ltc_cmd_t | cmd, | ||

| uint8_t * | data, | ||

| uint32_t | len | ||

| ) |

Write to LTC6811 in dasy-chain!

- Parameters

-

ltc LTC6811 Instance cmd Command PEC is generated automatically data Data to send PEC is not generated! Proper size must be selected to send to all Slave in the chain! len Size of Data

- Returns

- -1 on error 0 on ok

◆ ltc6811_writeRegister()

| int32_t ltc6811_writeRegister | ( | struct ltc6811 * | ltc, |

| ltc_cmd_t | cmd, | ||

| uint8_t * | newData, | ||

| uint8_t * | oldData | ||

| ) |

Write to LTC6811 Register

- Parameters

-

ltc LTC6811 Instance cmd Command PEC is generated automatically newData New Register Content (send to all selected slaves) Array must be 6 bytes! PEC is generated automatically oldData Old Register Content (send also to all not selected slaves) Array must be 6 bytes! PEC is generated automatically

- Returns

- -1 on error 0 on ok